半导体晶圆制造工艺解析,从原料到核心载体的全流程

半导体芯片作为现代工业体系的核心组成部分,被誉为“工业皇冠上的明珠”。而晶圆作为芯片制造的基础载体,其制备工艺直接决定了芯片的性能与良率。本文基于半导体产业技术逻辑,系统梳理晶圆制造的核心流程、产业分工体系及关键技术要点,为理解半导体产业链底层逻辑提供专业参考。

一、半导体产业分工体系与晶圆制备的定位

芯片制造涉及数百道精密工序,产业分工高度专业化,已形成清晰的产业链协作模式。从全流程视角,芯片制造可划分为芯片设计、晶圆制备、芯片制造(前端工艺)、封装测试(后端工艺)四大核心阶段,各阶段对应不同类型的市场主体,而晶圆制备是连接原料与芯片制造的关键环节。

(一)核心市场主体类型

1.Fabless(无晶圆厂设计企业)

专注于芯片电路设计与研发,不涉及制造环节,将设计方案交付代工厂生产。典型企业包括高通(Qualcomm)、英伟达(NVIDIA)、联发科(MediaTek)及华为海思等。此类企业的核心竞争力在于芯片架构设计与算法优化,但受限于代工厂工艺能力,其高端设计方案的落地依赖先进晶圆制造技术。

2.Foundry(晶圆代工厂)

作为专业制造实体,承接Fabless的生产订单,负责将设计图纸通过光刻、蚀刻等工艺“转移”至晶圆表面。全球头部代工厂包括中国台湾地区的台积电(TSMC)、中国大陆的中芯国际(SMIC)、华虹集团,以及联电(UMC)等。晶圆代工厂的工艺水平(如3nm、2nm制程)是半导体产业的核心瓶颈,直接影响区域芯片产业的竞争力。

3.OSAT(外包半导体组装测试企业)

负责对代工厂产出的“裸芯片(BareDie)”进行封装(提供物理保护与引脚引出)和测试(筛选合格产品),是芯片实现商用的最后环节。全球主流OSAT企业包括日月光(ASE)、长电科技(JCET)、通富微电(UTAC)、安靠(Amkor)等,其技术优势在于封装形式的多样化与测试效率的提升。

4.IDM(集成设备制造商)

覆盖芯片设计、晶圆制备、封装测试全流程,具备垂直整合能力。全球范围内具备完整IDM能力的企业较少,主要包括英特尔(Intel)、三星(Samsung)、德州仪器(TI)、意法半导体(STMicroelectronics)等。尽管IDM模式技术壁垒高,但受限于产业规模扩大与专业化分工趋势,Fabless+Foundry的协作模式已成为主流——例如AMD曾为IDM企业,后剥离制造业务转型Fabless,其原制造部门独立为全球五大代工厂之一的格芯(GlobalFoundries)。

二、半导体晶圆制备全流程(六大核心步骤)

晶圆制备以石英砂为初始原料,通过提纯、晶体生长、切割、精修等工艺,最终形成符合芯片制造要求的高纯度、高平整度薄片。整个过程需突破材料纯度、晶体结构、精密加工三大技术维度的极限。

(一)原料筛选与硅提纯:从石英砂到电子级硅(EGSi)

1.原料选择

晶圆的核心原料为硅(Si),其广泛存在于石英砂中(主要成分为二氧化硅SiO₂)。工业生产中需筛选硅含量≥99%的高纯度石英砂矿石,避免杂质引入后续工艺。

2.初级提纯(冶金级硅制备)

将石英砂与碳源(如焦炭)按特定比例混合,放入高温炉中加热至1400℃以上(硅的熔点为1410℃),通过化学反应去除氧元素,生成纯度≥98%的冶金级硅(MGSi)。此阶段产物主要用于工业领域,无法满足半导体要求。

3.深度提纯(电子级硅制备)

对冶金级硅进行氯化反应(生成三氯氢硅SiHCl₃)与蒸馏提纯,去除铁、铝、硼等杂质,最终得到纯度达99.9999999%~99.999999999%(9~11个“9”)的电子级硅(EGSi)。该纯度标准下,每百万个硅原子中允许的杂质原子不超过1个,远高于光伏产业所用太阳能级硅(SGSi,纯度4~6个“9”)的要求。

(二)单晶硅锭拉制:构建有序晶体结构

提纯后的硅为多晶硅(原子排列无序、缺陷较多),需通过晶体生长工艺转化为单晶硅(原子排列规则、电学性能稳定),主流技术为直拉法(CzochralskiMethod,简称CZ法),具体流程如下:

1.将高纯度多晶硅放入石英坩埚,加热至1410℃以上使其熔融,形成均匀的硅熔体;

2.将预先制备的单晶硅种子晶体(纯度与目标一致)缓慢浸入硅熔体,种子晶体作为“晶体生长模板”,引导周围硅原子按相同晶格结构排列;

3.同步控制种子晶体的旋转速度(保持熔体均匀性)与提拉速度:初始阶段以6mm/分钟的速度提拉约10cm,避免热冲击导致晶体缺陷;后续降低提拉速度,确保晶体结构稳定;

4.硅熔体随提拉过程逐渐凝固,最终形成直径约30cm、长度1~1.5m的圆柱形单晶硅锭(简称“硅锭”),其晶体结构完整性直接影响后续晶圆的电学性能。

(三)硅锭切割:制备初始晶圆薄片

硅锭需切割为特定厚度的薄片(即“裸晶圆”),核心要求为“高精度、低损耗”,主流技术分为两类:

1.多线锯切割

采用附着金刚石颗粒的高强度线材,通过高速往复运动对硅锭进行切割,可同时生成多片晶圆。该技术效率高、材料损耗率低(≤5%),适用于大规模量产,是当前8英寸、12英寸晶圆的主要切割方式。

2.内圆锯切割

锯片为内部镀金刚石的圆形刀片,通过高速旋转实现切割。该技术切割精度更高(厚度公差≤±5μm)、振动更小,适用于对平整度要求极高的特殊晶圆(如功率器件用晶圆),但效率相对较低,成本较高。

切割过程中需同步使用切割液(水基或油基),起到冷却、润滑及碎屑清除作用;同时严格控制环境温度(23±2℃)与振动(振幅≤0.1μm),避免硅片(脆性材料)碎裂。

(四)晶圆精修:实现纳米级平整度

裸晶圆表面粗糙且存在切割残留(如微裂纹、切割液),需通过多道精修工艺提升表面质量,核心步骤包括:

1.边缘研磨

采用专用研磨设备对晶圆边缘进行圆弧化处理,消除锋利边角——高纯度硅的脆性较高,锋利边缘易在后续工艺中因应力集中导致碎裂,研磨后晶圆边缘曲率半径需符合SEMI规范(如12英寸晶圆边缘半径≥0.5mm)。

2.化学蚀刻

将晶圆浸泡于亚硝酸(HNO₂)与乙酸(CH₃COOH)的混合溶液中,通过化学反应去除表面微裂纹与切割痕迹,修复晶体表层缺陷,蚀刻深度通常控制在5~10μm。

3.化学机械抛光(CMP)

实现晶圆表面纳米级平整的核心工艺,原理为“化学作用+机械研磨”协同:

化学阶段:抛光液中的化学试剂(如二氧化硅溶胶)与硅表面反应,生成易去除的软化层(如氧化硅);

机械阶段:抛光垫(如聚氨酯材质)在一定压力与转速下运动,带动抛光液中的磨料颗粒(如纳米级二氧化硅)研磨表面,去除软化层与残留杂质。

CMP后晶圆表面粗糙度需≤0.1nm,平整度误差≤1nm,为后续光刻工艺(需高精度图案转移)奠定基础。

(五)超洁净清洗:消除污染物

CMP后晶圆表面可能残留抛光液、磨料颗粒等污染物,而半导体制造中“单个微米级杂质即可导致芯片失效”,因此需进行超洁净清洗:

1.采用酸碱交替冲洗(如稀盐酸去除金属杂质、稀氨水去除有机残留),消除不同类型污染物;

2.使用超纯水(电阻率≥18.2MΩ·cm的RO/DI水)进行多次冲洗,确保表面无化学残留;

3.整个清洗过程在Class1级洁净室(每立方米空气中粒径≥0.1μm的尘埃颗粒≤1个)内进行,避免环境污染物附着。

(六)质量检测与分类:确保合规性

清洗后的晶圆(称为“抛光晶圆”)需通过严格检测,确保符合芯片制造要求,检测项目及标准如下:

通过检测的晶圆需进行标识:边缘设置平边(Flat)或缺口(Notch),用于后续工艺中晶体取向定位;背面刻制唯一序列号,实现全生命周期追溯。不合格晶圆需返工(如重新抛光)或报废,确保流入芯片制造环节的晶圆良率≥99%。

三、晶圆制造关键问题解析

(一)晶圆尺寸选择的逻辑

当前主流晶圆尺寸包括8英寸(200mm)与12英寸(300mm),尺寸选择需平衡“成本效益”与“制造难度”:

成本优势:晶圆尺寸越大,单位面积可制造的芯片数量越多——在相同工艺下,12英寸晶圆的表面积为8英寸的2.25倍,可生产的芯片数量约为8英寸的2.5倍(需扣除切割道与边缘浪费),单位芯片成本降低30%~50%;

技术难度:尺寸越大,制造难度呈指数级提升——例如12英寸硅锭拉制需更精准的温度控制(波动≤±0.1℃)与提拉速度控制(波动≤±0.1mm/分钟),切割时易因应力不均导致碎裂,因此12英寸晶圆的设备投入与工艺控制要求远高于8英寸。

目前,12英寸晶圆主要用于高端逻辑芯片(如手机SoC、PCCPU)与存储芯片(如NANDFlash、DRAM),8英寸晶圆多用于功率器件、射频芯片等领域,更小尺寸(≤6英寸)晶圆已逐步退出主流市场。

(二)晶圆圆形设计的必然性

尽管芯片为方形,但晶圆采用圆形设计,核心原因在于制造工艺与实用性的双重约束:

1.制造工艺决定:直拉法拉制的硅锭为圆柱形,切割后自然形成圆形晶圆——若采用方形硅锭,需通过复杂的晶体生长控制,当前技术无法实现高效量产;

2.加工便利性:圆形晶圆在旋转加工(如光刻、CMP)时受力均匀,可避免方形晶圆边角导致的应力集中,降低碎裂风险;运输过程中圆形结构也能减少碰撞损伤;

3.材料利用率优化:看似方形晶圆可匹配方形芯片,但实际生产中芯片需按阵列排列并预留切割道。通过数学建模计算,圆形晶圆的边缘浪费率(约15%)低于方形晶圆(约20%),材料利用率更优。

(三)晶圆材料的多元化趋势

硅是当前晶圆的主流材料(占比超90%),但半导体材料已发展至第四代,不同材料适用于不同场景:

第一代半导体:硅(Si)、锗(Ge)——硅因储量丰富(地壳中含量28%,仅次于氧)、电学性能稳定、制造工艺成熟,成为逻辑芯片与存储芯片的唯一选择;锗因漏电流大、热稳定性差,已逐步被硅替代;

第二代半导体:砷化镓(GaAs)、磷化铟(InP)——具备高频、高电子迁移率特性,适用于射频芯片(如5G基站)、光通信芯片(如光纤模块);

第三代半导体:氮化镓(GaN)、碳化硅(SiC)——具备耐高温(≥300℃)、耐高压(≥1000V)特性,适用于新能源汽车功率模块、快充设备、智能电网;

第四代半导体:氧化镓(Ga₂O₃)、金刚石(C)——击穿场强与热导率远超第三代材料,适用于航空航天、核能等极端环境,但制造工艺尚未成熟,暂未实现量产。

硅的主导地位源于“性能成本工艺”的平衡:其电学性能可满足多数场景需求,且产业链(设备、材料、工艺)成熟度远高于其他材料,短期内难以被替代。

四、结语:晶圆制造的设备支撑与产业赋能

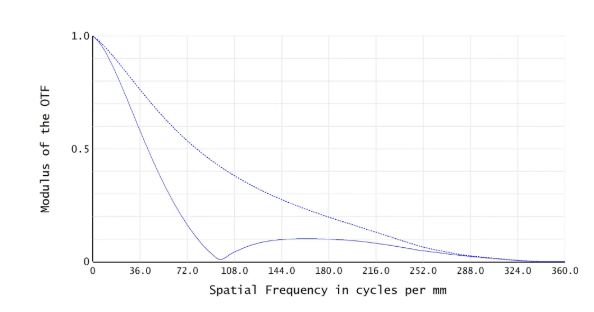

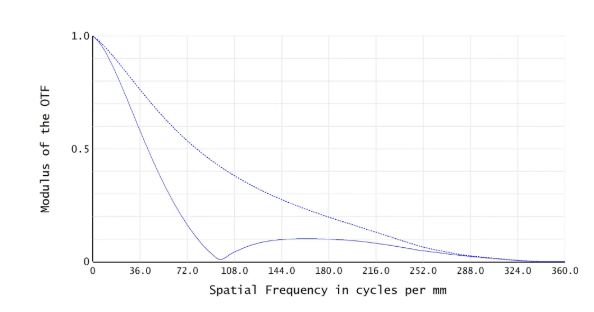

半导体晶圆制备的精密性,不仅依赖工艺优化,更需高端检测与装配设备的支撑——尤其是在大口径、高负载晶圆(如功率器件用8英寸/12英寸晶圆、特殊材料晶圆)的制造中,中心偏差、曲率半径、光学传递函数(MTF)等参数的精准测量,直接决定晶圆后续加工的良率与芯片最终性能。

针对这一需求,德国TRIOPTICS研发的OptiCentric®UP大口径中心偏差测量仪,为半导体晶圆及光学系统制造提供了专业解决方案。该设备涵盖OptiCentric®300UP/600UP/800UP三大型号,核心优势显著:其一,精度达±0.2μm(或±2″),重复精度±0.1μm(或±1″),测量结果可追溯至国际标准,满足半导体级高精度要求;其二,支持最大直径800mm、最大重量1200KG的样品测量,适配大口径晶圆及多镜片镜头组的检测需求;其三,具备全自动软件操作、多波长测量功能,可拓展平面光学元件角度、镜面间隔、有效焦距(EFL)、后截距(BFL)及轴上MTF测量等能力,实现“检测装配验证”一体化。

对于我国半导体产业而言,此类高精度设备的引入与应用,可有效弥补高端检测设备短板,助力晶圆制造企业提升工艺控制水平、降低不良率,为高端芯片自主可控提供关键设备支撑。如需了解该设备的详细技术参数与应用方案,可访问欧光科技官网(https://www.europtics.com.cn/productinfo/2071255.html)获取专业咨询。

-

麻省理工学院突破光学原子钟小型化瓶颈:集成螺旋腔激光器实现芯片级原子询问

美国麻省理工学院林肯实验室WilliamLoh与RobertMcConnell团队在《NaturePhotonics》(2025年19卷3期)发表重大研究成果,成功实现基于集成超高品质因子螺旋腔激光器的光学原子钟原子询问,为光学原子钟走出实验室、实现真正便携化铺平了道路。这一突破标志着光学原子钟向全集成、可大规模制造的先进时钟系统迈出关键一步,有望彻底改变导航、大地测量和基础物理研究等领域的时间测量技术格局。

2026-04-08

-

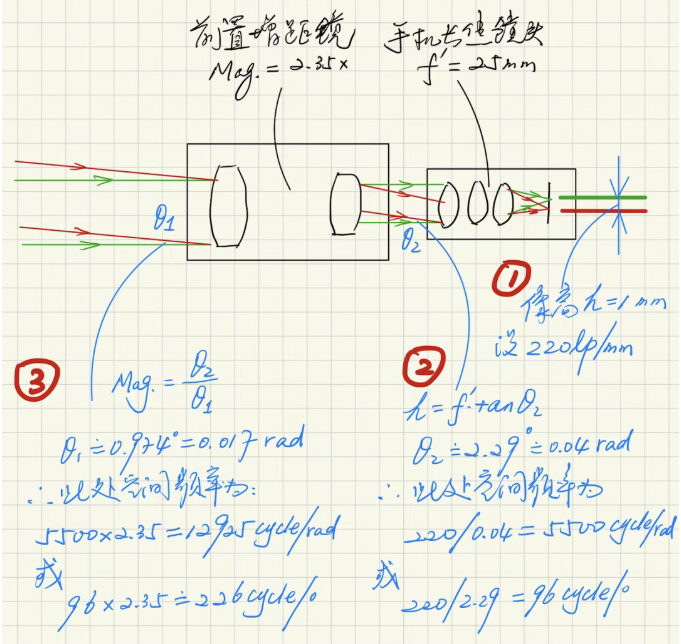

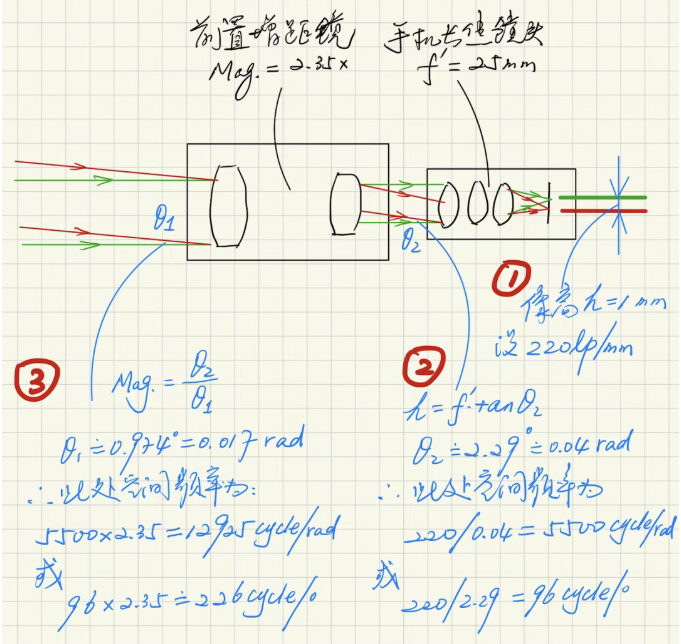

手机长焦增距镜无焦光学系统MTF测试的空间频率换算研究

在手机成像技术向高倍长焦方向快速发展的背景下,手机长焦增距镜作为提升手机长焦拍摄能力的核心无焦光学器件,其成像质量的精准评价成为光学检测领域的重要课题。光学传递函数(MTF)是衡量光学系统成像质量的核心指标,而手机长焦增距镜属于望远镜类无焦光学系统,其MTF测试采用的角频率单位与常规无限-有限共轭光学系统的线频率单位存在本质差异。为实现两类单位的精准转换、保证MTF测试结果的有效性与实际应用价值,本文从无焦光学系统特性与测量工具出发,明确空间频率不同单位的核心属性,结合实际案例完成换算推导,梳理换算关键要点,为手机长焦增距镜的MTF检测及光学性能评价提供严谨的技术参考。

2026-04-08

-

非线性光学晶体:现代激光技术的核心功能材料

非线性光学晶体作为实现激光频率转换、光束调控及光场非线性效应的关键功能材料,突破了传统激光器件输出波长受限的技术瓶颈,是支撑紫外/深紫外激光、中红外激光、超快激光及量子光源等先进激光系统发展的核心基础部件。本文系统阐述非线性光学效应的物理机制、主流非线性光学晶体的材料特性与相位匹配技术,梳理其在科研探测、精密制造、生物医疗、光通信及国防安全等领域的典型应用,并展望该类材料未来的发展方向,为相关领域技术研究与工程应用提供参考。

2026-04-08

-

波前像差、点扩散函数(PSF)与调制传递函数(MTF)的关联解析

在光学成像领域,波前像差(WavefrontAberration)、点扩散函数(PointSpreadFunction,PSF)与调制传递函数(ModulationTransferFunction,MTF)是描述光学系统成像质量的核心参数。三者相互关联、层层递进,共同决定了系统的最终成像效果与视觉质量,但其内在联系常令初学者困惑。本文将从概念本质出发,系统解析三者的关联逻辑,结合具体实例深化理解,为相关领域的学习与应用提供清晰指引。

2026-04-07

-

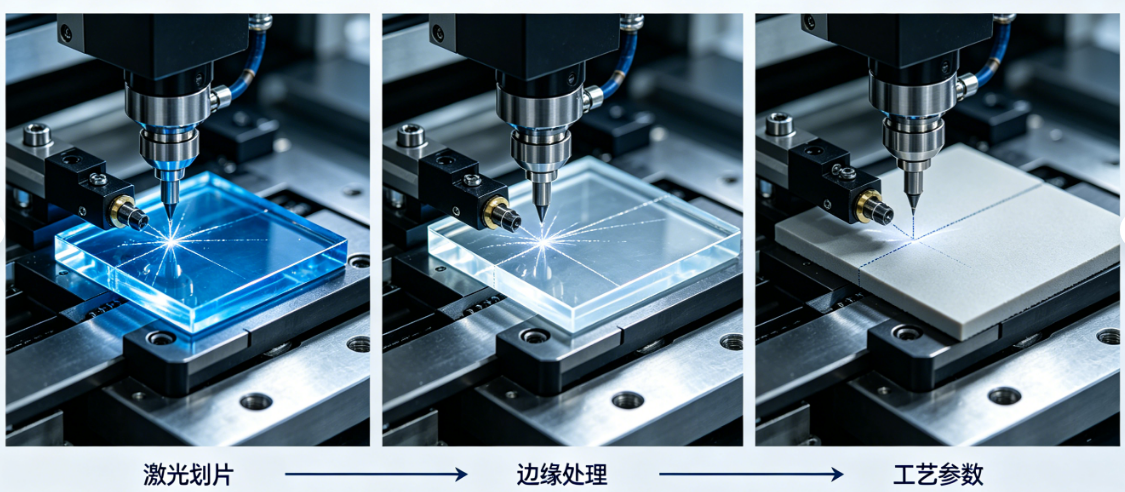

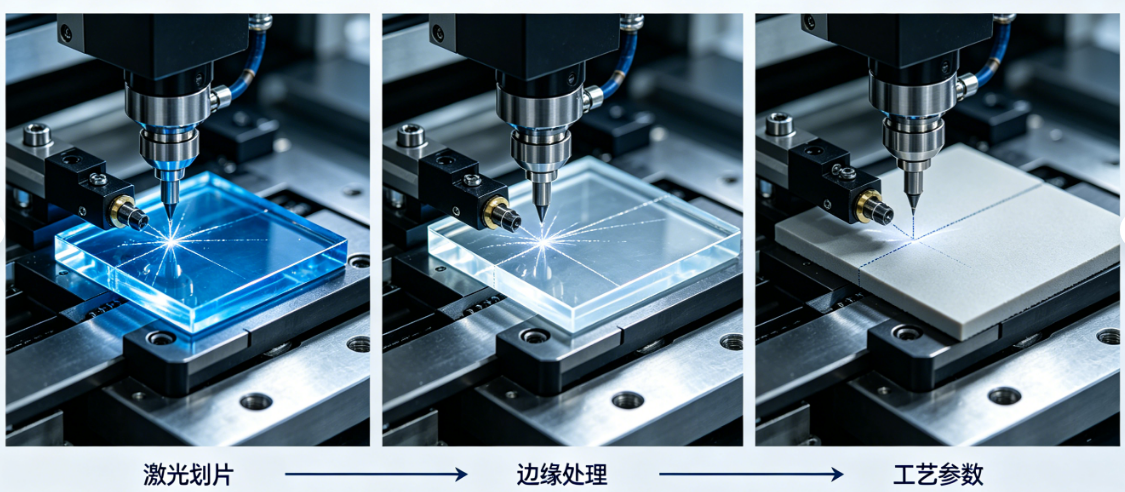

非硅特种材料精密划片工艺技术方案

在半导体封装、光学器件、电子元器件等高端制造领域,蓝宝石、玻璃、陶瓷等非硅特种材料的应用日益广泛。此类材料物理特性与传统硅片差异显著,常规硅片划片工艺无法直接适配,易出现崩边、裂纹、刀具损耗大、良品率偏低等问题。结合材料特性与实际量产经验,针对蓝宝石、玻璃、陶瓷三大类核心材料,形成专业化精密划片工艺解决方案。

2026-04-07