半导体制造工艺解析,从硅锭到芯片的核心流程与技术演进

半导体器件的制造过程涉及多个精密环节,其中硅片、硅晶圆、裸片及芯片是贯穿全流程的关键形态。本文将从材料特性、工艺演进及技术标准等维度,系统阐述四者间的内在关联与制造工艺的阶段性特征。

一、基础材料的形态演变

高纯度硅锭制备

通过西门子法等工艺将石英砂提纯至9-11N超纯多晶硅后,采用Czochralski直拉法或区熔法生长单晶硅锭。该过程需严格控制温度梯度与旋转速率,以确保晶体轴向位错密度低于1个/cm²。

初始形态切割

直径从早期的2英寸(50.8mm)逐步升级至当前主流的300mm(12英寸),晶圆尺寸的扩大使单片产出芯片数量提升近3倍,单位成本降低约40%。切割工艺采用金刚石线锯,200mm以下硅锭保留平边定位标识,更大尺寸则采用环形凹槽设计。

二、精密加工与表面处理

硅片向晶圆的转化

经倒角(EdgeGrinding)、双面研磨(Lapping)及化学机械抛光(CMP)三重处理后,300mm晶圆表面粗糙度可达Ra<20nm,相当于在地球尺度下起伏不足3米。此阶段的平整度直接影响光刻工艺的分辨率极限。

关键工艺指标

现代晶圆制造要求:

表面颗粒物控制:<0.1μm(ISOClass1标准)

氧化层厚度均匀性:<±1%

热膨胀系数匹配:与铜互连层实现热应力补偿

三、集成电路构建与检测

微纳加工工艺

通过数十层光刻、刻蚀及离子注入,在晶圆表面形成阵列式裸片(Die)。典型FinFET工艺包含超过30道掩模版工序,最小特征尺寸已达3nm节点。每个裸片集成数亿晶体管,互连线总长度可绕地球数周。

质量管控体系

晶圆测试采用探针卡接触焊盘阵列,测试项目涵盖电性参数、可靠性及良率预测。先进封装技术如3DIC采用TSV通孔互联,使芯片间带宽提升100倍以上。

四、终端产品实现路径

划片与分选

激光切割或金刚石划片将晶圆分离为独立裸片,良品率受制程稳定性影响显著。高端逻辑芯片良率通常>80%,而存储器类芯片因高密度存储单元特性,良率控制在60%-70%区间。

封装技术迭代

从传统引线键合(WireBonding)到倒装芯片(FlipChip),再到系统级封装(SiP),封装技术不断突破散热与I/O密度瓶颈。2.5D/3D封装使单位面积集成度提升4倍,传输速率突破112Gbps。

五、技术演进趋势

当前半导体制造呈现三大发展方向:

异构集成:Chiplet技术实现算力模块灵活组合,预计2025年市场规模达58亿美元

材料创新:碳化硅、氮化镓等宽禁带半导体拓展功率器件应用边界

制程微缩:EUV光刻技术推动逻辑芯片进入埃米时代

从硅砂到芯片的蜕变,本质上是人类对物质微观世界的极致操控。每一代工艺节点的突破都伴随着材料科学、光学工程及计算模拟技术的协同进步。未来,随着AI驱动的智能制造与量子计算的兴起,半导体制造将继续向更高集成度、更低功耗及更强功能性的方向演进。

相关内容推荐:半导体光刻物镜装调

-

麻省理工学院突破光学原子钟小型化瓶颈:集成螺旋腔激光器实现芯片级原子询问

美国麻省理工学院林肯实验室WilliamLoh与RobertMcConnell团队在《NaturePhotonics》(2025年19卷3期)发表重大研究成果,成功实现基于集成超高品质因子螺旋腔激光器的光学原子钟原子询问,为光学原子钟走出实验室、实现真正便携化铺平了道路。这一突破标志着光学原子钟向全集成、可大规模制造的先进时钟系统迈出关键一步,有望彻底改变导航、大地测量和基础物理研究等领域的时间测量技术格局。

2026-04-08

-

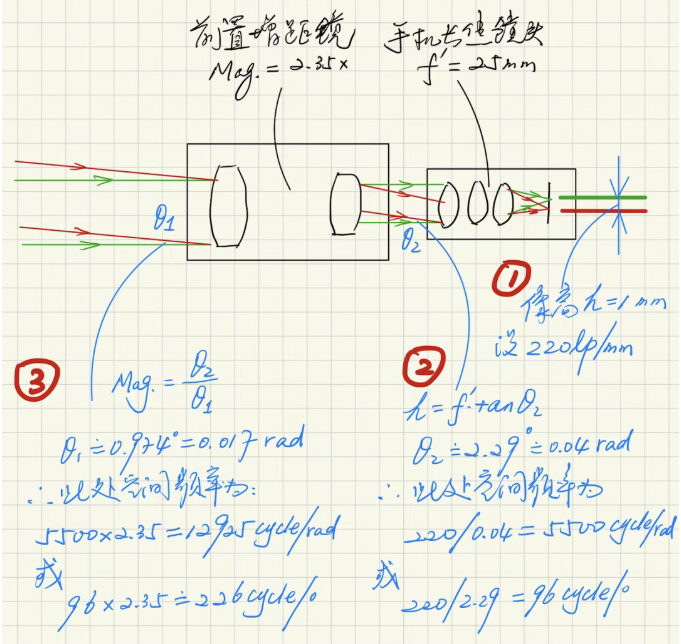

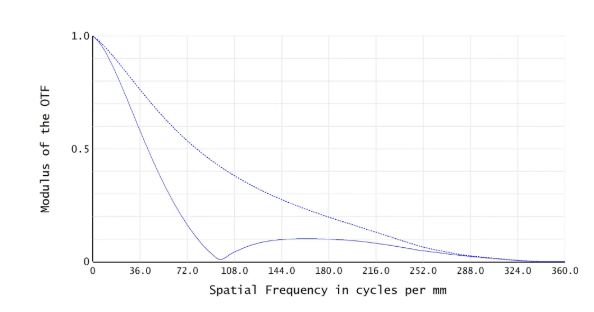

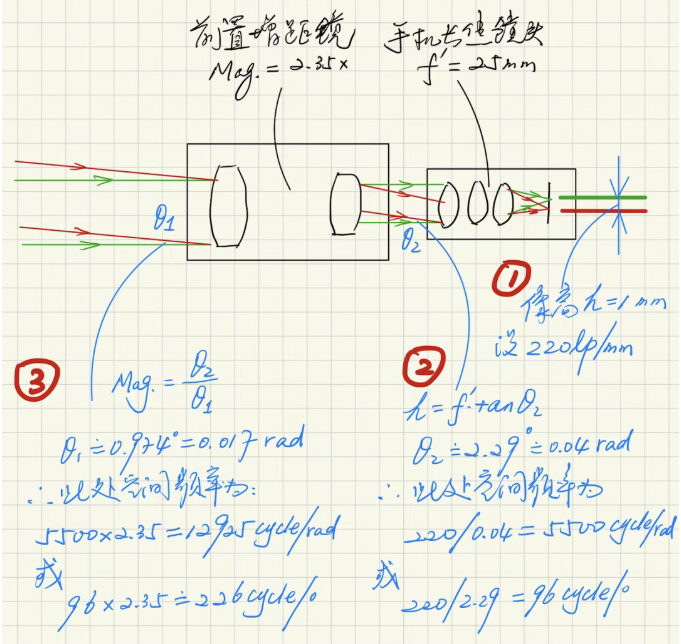

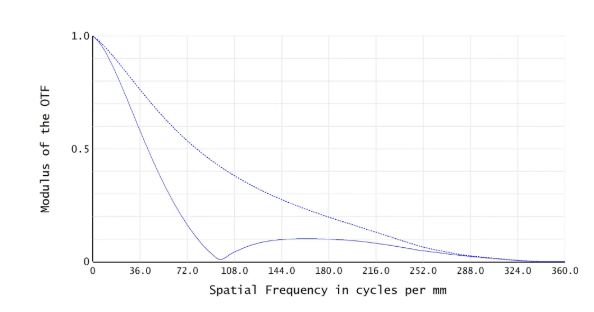

手机长焦增距镜无焦光学系统MTF测试的空间频率换算研究

在手机成像技术向高倍长焦方向快速发展的背景下,手机长焦增距镜作为提升手机长焦拍摄能力的核心无焦光学器件,其成像质量的精准评价成为光学检测领域的重要课题。光学传递函数(MTF)是衡量光学系统成像质量的核心指标,而手机长焦增距镜属于望远镜类无焦光学系统,其MTF测试采用的角频率单位与常规无限-有限共轭光学系统的线频率单位存在本质差异。为实现两类单位的精准转换、保证MTF测试结果的有效性与实际应用价值,本文从无焦光学系统特性与测量工具出发,明确空间频率不同单位的核心属性,结合实际案例完成换算推导,梳理换算关键要点,为手机长焦增距镜的MTF检测及光学性能评价提供严谨的技术参考。

2026-04-08

-

非线性光学晶体:现代激光技术的核心功能材料

非线性光学晶体作为实现激光频率转换、光束调控及光场非线性效应的关键功能材料,突破了传统激光器件输出波长受限的技术瓶颈,是支撑紫外/深紫外激光、中红外激光、超快激光及量子光源等先进激光系统发展的核心基础部件。本文系统阐述非线性光学效应的物理机制、主流非线性光学晶体的材料特性与相位匹配技术,梳理其在科研探测、精密制造、生物医疗、光通信及国防安全等领域的典型应用,并展望该类材料未来的发展方向,为相关领域技术研究与工程应用提供参考。

2026-04-08

-

波前像差、点扩散函数(PSF)与调制传递函数(MTF)的关联解析

在光学成像领域,波前像差(WavefrontAberration)、点扩散函数(PointSpreadFunction,PSF)与调制传递函数(ModulationTransferFunction,MTF)是描述光学系统成像质量的核心参数。三者相互关联、层层递进,共同决定了系统的最终成像效果与视觉质量,但其内在联系常令初学者困惑。本文将从概念本质出发,系统解析三者的关联逻辑,结合具体实例深化理解,为相关领域的学习与应用提供清晰指引。

2026-04-07

-

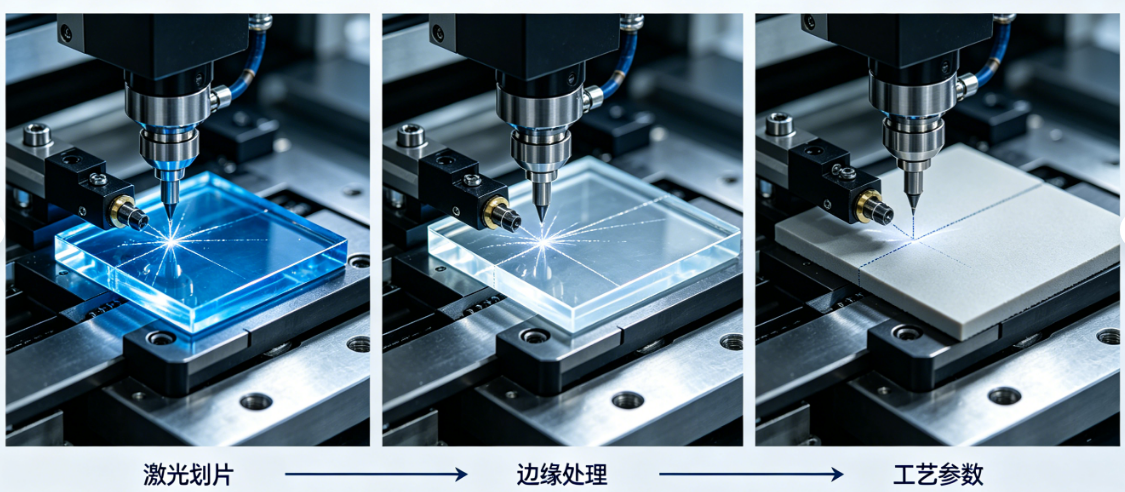

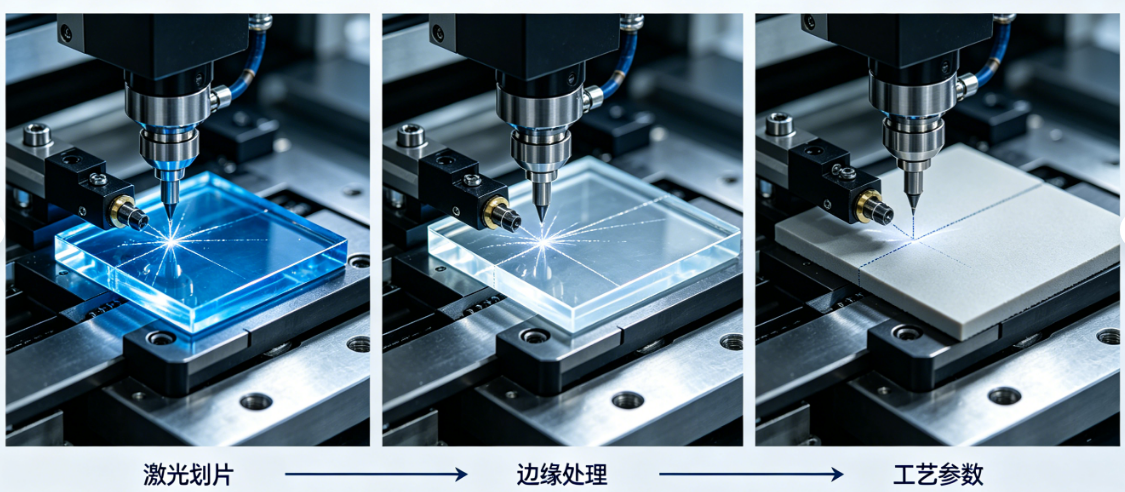

非硅特种材料精密划片工艺技术方案

在半导体封装、光学器件、电子元器件等高端制造领域,蓝宝石、玻璃、陶瓷等非硅特种材料的应用日益广泛。此类材料物理特性与传统硅片差异显著,常规硅片划片工艺无法直接适配,易出现崩边、裂纹、刀具损耗大、良品率偏低等问题。结合材料特性与实际量产经验,针对蓝宝石、玻璃、陶瓷三大类核心材料,形成专业化精密划片工艺解决方案。

2026-04-07