晶圆减薄技术的工艺演进与半导体封装应用研究

在半导体制造领域,晶圆减薄工艺作为封装环节的核心技术,其技术进步直接影响着芯片的可靠性、集成密度及电子设备的微型化进程。从4英寸晶圆520微米的原始厚度到叠层封装中30微米以下的极限薄度控制,这一微米级精度的工艺变革,本质上是材料科学、精密加工与半导体封装技术的交叉融合。本文将系统阐述晶圆减薄的技术价值、工艺体系及前沿创新,为半导体封装领域的技术研发提供参考。

一、晶圆减薄的技术价值与应用场景分析

(一)封装工艺中的多维度技术需求

在半导体前端制造阶段,晶圆需保持特定厚度以确保工艺稳定性:8英寸晶圆725微米的原始厚度可抵御光刻、刻蚀等工艺中的机械应力与热应力,而12英寸晶圆775微米的规格则为复杂制程提供结构支撑。进入封装环节后,传统厚晶圆的高硬度特性成为瓶颈——机械划片时易出现裂片现象,不良率可高达15%以上。通过减薄工艺将晶圆厚度降至150微米以下,可使材料硬度降低40%,配合激光切割技术,划片精度可提升至±5微米,显著优化封装良率。

电子设备的轻薄化趋势进一步凸显减薄工艺的战略价值。在智能手机3D封装中,晶圆厚度每削减100微米,主板空间利用率可提升8%,这对追求极致集成度的移动终端至关重要。散热性能优化方面,减薄工艺可使芯片热传导路径缩短30%,在5G芯片等高功耗场景中,结温可降低1215℃,有效提升器件长期运行的可靠性。

(二)不同封装结构的差异化厚度要求

封装技术的多元化发展催生了减薄工艺的梯度化需求:

DIP封装需保留约300微米的厚度以维持机械强度;

BGA封装的减薄区间通常控制在120250微米,平衡电气性能与结构稳定性;

先进叠层封装中,芯片厚度需薄至30微米以下,此时减薄精度需控制在±1微米以内,相当于人类头发丝直径的1/50,对工艺提出极高要求。

二、晶圆减薄技术体系与工艺特性比较

(一)主流减薄工艺的技术原理与应用边界

1.磨削减薄技术

作为当前主流工艺,磨削减薄通过金刚石砂轮的高速旋转实现材料去除,300mm硅片从750微米减至180微米的典型加工周期仅需90秒,厚度均匀性控制在±0.3微米。TAIKO工艺的创新在于通过边缘保护环设计,保留晶圆边缘3mm区域,使薄型晶圆的破损率降低70%,尤其适用于大尺寸硅片加工。然而,磨削工艺会在表面产生510微米的损伤层,需后续工艺修复。

2.化学机械抛光(CMP)

该工艺通过二氧化硅磨料与酸性抛光液的协同作用,实现纳米级表面处理,粗糙度可降至Ra0.2纳米以下。但加工效率较低(每小时材料去除量仅23微米),主要用于精密抛光阶段,如高端芯片的表面平整度优化。

3.湿法化学腐蚀工艺

利用氢氧化钾等腐蚀液与硅片的化学反应实现减薄,其优势在于无损伤加工,可消除晶格位错并使硅片强度提升15%。但需对晶圆正面进行精密保护,且对磨削条纹的校正能力有限,常作为磨削工艺的辅助手段。

4.常压等离子腐蚀(ADPE)

作为干法工艺的代表,ADPE通过CF₄气体电离产生氟自由基,与硅反应生成气态SiF₄,单次可去除50100微米材料。该工艺无需正面保护,在加工带有硅通孔(TSV)的三维封装晶圆时,可使结构损伤率降低90%,成为先进封装的关键技术。

(二)组合工艺的协同优化策略

实际生产中,多采用“粗加工精加工”的组合工艺模式。以300μm硅片减薄至120μm为例:

1.首先通过磨削工艺快速去除大部分材料,将厚度削减至160μm左右;

2.随后根据产品需求选择后续处理:

对平整度要求极高的芯片,采用“磨削+CMP”组合,可将表面粗糙度控制在纳米级;

处理复杂微结构超薄晶圆时,“磨削+ADPE”组合既能高效减薄,又能保证结构完整性。

三、前沿减薄工艺的创新突破与技术路径

(一)应力控制技术的革新

传统减薄工艺中,晶圆厚度低于100微米时易发生翘曲变形,“先划片后减薄(DBG)”与“减薄划片(DBT)”技术的出现有效解决了这一难题。DBG工艺先在晶圆正面切割出1/3厚度的沟槽,通过预切割优化应力分布,使翘曲度降低60%;DBT技术则结合ADPE腐蚀工艺,利用各向同性刻蚀特性消除磨削损伤,同时修复芯片边缘微裂纹,使抗碎裂性能提升3倍。

(二)高精度加工技术的集成应用

在DBT技术基础上发展的“DBG+DAF切割”工艺,通过在晶圆背面粘贴直接黏合膜(DAF)并单独进行激光切割,将晶粒对齐精度提升至±2微米,为10微米以下超薄芯片加工提供了技术支撑,使芯片堆叠层数突破100层成为可能。

四、晶圆加工减薄工艺流程的精密控制体系

(一)全流程工艺控制要点

1.表面防护贴膜

采用紫外线解胶型保护膜时,365nm波长照射可使胶层黏性在10秒内从500g/25mm降至50g/25mm;贴膜机滚轴压力需精确控制在0.20.3MPa,确保气泡率低于0.1%。

2.背面研磨加工

采用“粗磨精磨”双阶段工艺:

粗磨使用300粒度砂轮,材料去除速率达50微米/分钟;

精磨切换至1200粒度砂轮,表面粗糙度控制在Ra10纳米以内;

300mm晶圆研磨压力维持在0.50.8N/cm²,保证厚度均匀性。

3.去膜工艺

离子风环境下,剥离膜黏性需匹配保护膜(通常100200g/25mm),剥离速度控制在50100mm/min;针对30微米以下超薄晶圆,采用50℃冷冻去膜技术,实现无应力剥离。

五、技术发展趋势与产业影响

从100mm硅片的传统磨削到300mm晶圆的自旋转减薄,从单一工艺到“磨削+等离子腐蚀”的复合技术,晶圆减薄工艺的演进始终与半导体产业的需求同步。随着3DIC、扇出型封装等先进技术的普及,10微米级超薄芯片加工将成为主流,这要求减薄工艺在材料去除效率、表面损伤控制及应力管理等方面实现进一步突破。

作为半导体封装的关键基础工艺,晶圆减薄技术的进步不仅推动着电子设备的微型化与高性能化,更对摩尔定律的延续具有重要意义。在人工智能、物联网等前沿领域,微米级精度的减薄工艺正成为提升芯片集成密度与系统性能的核心支撑,引领半导体制造向更高维度发展。

-

超硬AR与普通AR抗反射膜的核心差异解析

在光学显示与光学器件领域,AR抗反射膜作为提升画面清晰度、优化光学性能的关键组件,应用场景日益广泛。目前市场上的AR抗反射膜主要分为普通AR与超硬AR两类,二者虽均以“减反增透”为核心目标,但在性能表现、适用场景等方面存在显著差距。本文结合膜层材料、结构设计、工艺路线等核心维度,系统解析两类AR膜的本质区别,为行业应用与选型提供参考。

2026-04-10

-

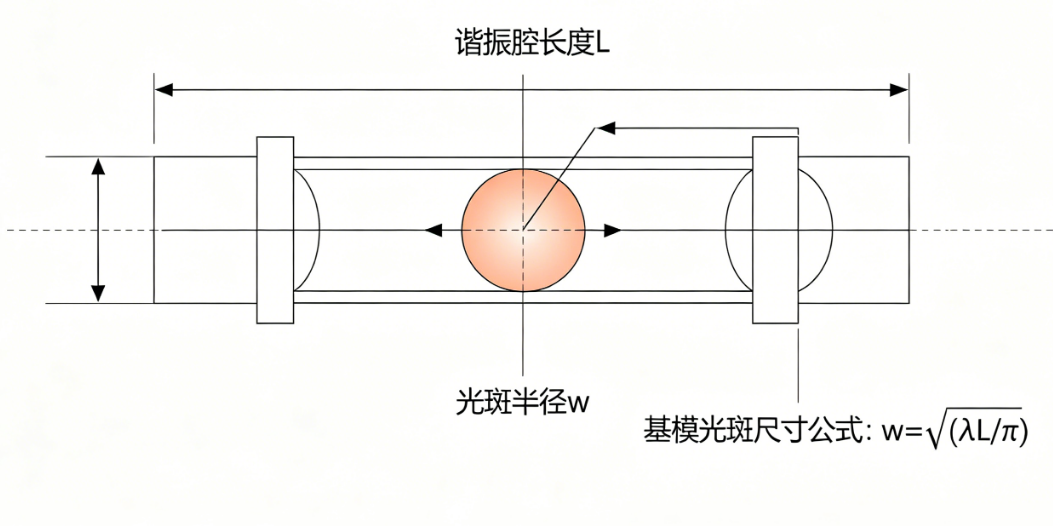

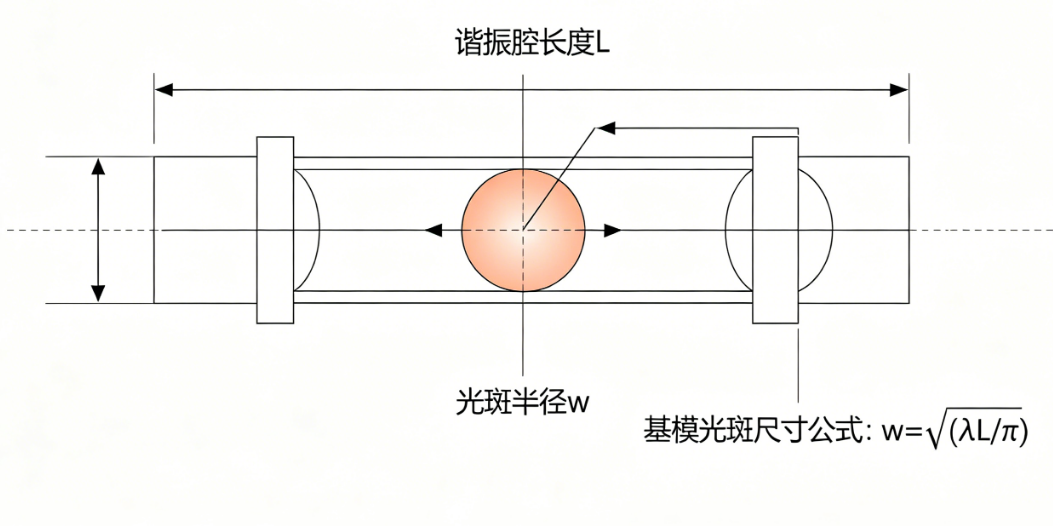

固体激光器谐振腔内光斑尺寸计算方法及工程应用

在固体激光器设计与性能优化中,谐振腔内光斑大小分布是决定光束质量、元件耐受功率及系统稳定性的核心参数。受增益介质热效应、腔型结构与光学元件排布等因素影响,腔内光斑尺寸并非固定值,需通过系统化建模与传输计算实现精准求解。本文基于热透镜等效模型与ABCD传输矩阵理论,系统阐述固体激光器谐振腔内光斑尺寸的完整计算流程、稳定性判据及工程应用价值,为激光器光学设计提供理论参考。

2026-04-10

-

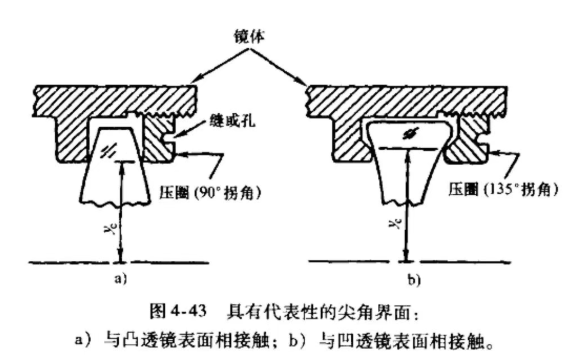

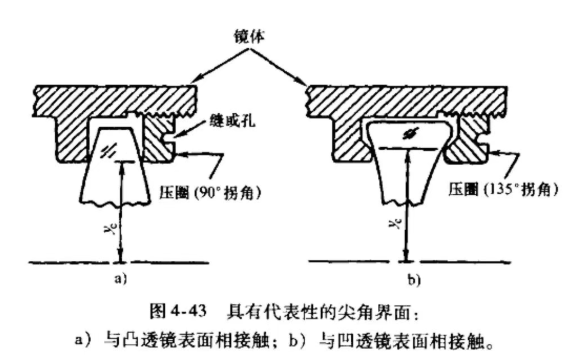

光学镜头装配中的5种光机界面接触方式:原理、特性与工程应用

光学镜头的装配精度直接决定了成像系统的最终性能,而光机界面作为光学元件与机械支撑结构的连接纽带,其设计与选择对同轴度控制、应力分布、热稳定性及长期可靠性具有决定性影响。在《光机系统设计》等权威著作中,将光机界面接触方式归纳为五大类:尖角界面、相切界面、超环面界面、球形界面及倾斜界面。本文系统解析这五种界面的设计原理、技术特性与工程应用场景,为光学工程师提供精准的选型参考。

2026-04-10

-

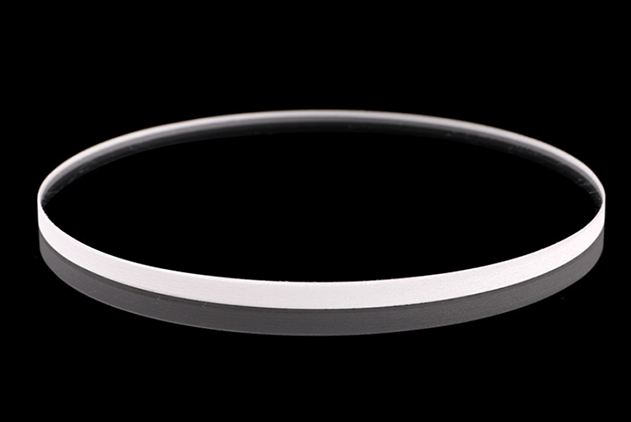

光学玻璃分类及K9玻璃特性解析

光学玻璃作为制造光学仪器核心部件的关键材料,广泛应用于光学透镜、棱镜、平面镜等产品的生产,其性能直接决定了光学仪器的成像质量与使用效果。本文将系统阐述光学玻璃的定义范畴、国家标准分类,并重点解析应用广泛的K9玻璃的核心特性,以及其与普通玻璃的本质区别

2026-04-09

-

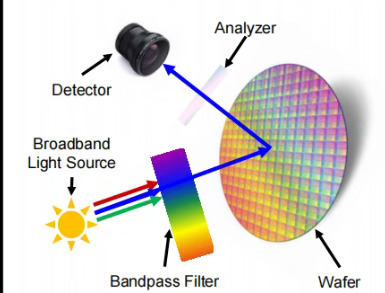

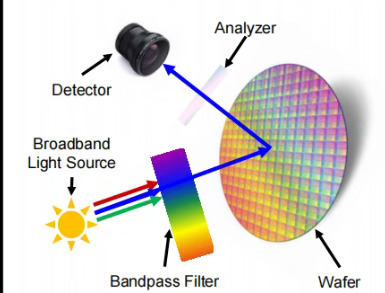

激光驱动光源(LDLS)技术原理及在半导体晶圆检测中的应用

随着半导体制造工艺持续向先进制程迭代,晶圆缺陷检测、薄膜厚度测量、光学计量等环节对光源的亮度、光谱范围、稳定性与空间相干性提出了愈发严苛的要求。传统氙灯、汞灯等常规光源在亮度、紫外输出及长期稳定性上已难以匹配高速、高精度检测需求。激光驱动光源(Laser-DrivenLightSource,LDLS)凭借超高亮度、宽谱连续输出与优异稳定性,成为先进半导体晶圆检测领域的核心关键光源,其技术特性与应用价值日益凸显。

2026-04-09