晶圆为何需要减薄?解析半导体制造中的关键工艺

在半导体产业链的精密体系中,晶圆减薄作为衔接前段制程与后段封装的核心环节,其技术价值贯穿于芯片制造的全生命周期。这项以微米级精度调控晶圆厚度的工艺,不仅是应对电子设备微型化趋势的必然选择,更是突破芯片性能瓶颈的关键技术路径。

一、厚度控制的双重逻辑:制造稳定性与封装微型化的平衡

在晶圆制造的前段制程(硅片加工阶段),维持特定厚度是保障工艺可靠性的基础。以300mm(12英寸)晶圆为例,其标准厚度设定为775μm,这一参数设计旨在满足光刻、离子注入等高温工艺对机械强度的要求,有效抵御传输过程中的翘曲风险。不同尺寸晶圆的厚度标准呈现阶梯式分布:150mm晶圆为675μm,200mm晶圆为725μm,较大的物理厚度为复杂制造工艺提供了必要的结构支撑。

进入后段封装阶段,厚度需求发生显著转变。为适配移动终端、可穿戴设备等场景对紧凑空间的需求,晶圆需通过减薄工艺将厚度压缩至100200μm,在3DIC等先进封装技术中,甚至需降至30μm以下(约为人类头发丝直径的1/3)。这种“前厚后薄”的工艺逻辑,本质是在制造可行性与终端产品性能之间构建最优解。

二、减薄工艺的技术价值:从物理尺寸到性能体系的全面提升

晶圆减薄的技术价值体现在封装优化、性能增强与可靠性提升的多维协同:

封装结构优化:厚度降低可使芯片体积缩小30%以上,为电子设备内部空间分配提供更多可能。同时,减薄后的晶圆在划片工序中崩边、崩角等缺陷发生率降低40%,显著提升封装良率。

芯片性能增强:热传导路径的缩短使高功耗芯片(如CPU/GPU)的散热效率提升25%,有效缓解热管理压力;寄生电容与电阻的减少可降低15%的高频信号传输损耗,配合背面金属化工艺,信号完整性得到显著改善。

可靠性提升:内部应力的降低使芯片在长期工作中的破裂风险下降50%,尤其适用于车载电子、工业控制等对可靠性要求严苛的场景。

三、精密制造的技术流程:从微米级磨削到原子级抛光的三阶工艺

晶圆减薄是一项基于微米级精度控制的系统工程,其技术流程可划分为三个关键阶段:

1.预处理工序:首先通过化学清洗去除晶圆表面污染物,随后沉积SiO₂或SiN钝化层以保护电路,最后采用临时键合技术将晶圆固定于载具,为后续加工提供机械支撑与保护。

2.分层加工工艺:粗磨阶段使用高速金刚石砂轮,以物理磨削方式快速去除大部分材料,将厚度误差控制在±10μm;精磨阶段切换为细砂轮,通过低转速修整使表面粗糙度(Ra)低于0.1μm;对于超高精度需求场景(如3D封装),需进一步采用化学机械抛光(CMP)或湿法蚀刻,将表面平整度控制在1nm以内,接近原子级光滑标准。

3.后处理环节:通过化学清洗去除残留磨料与化学试剂后,利用激光干涉仪等设备对晶圆厚度和平坦度进行精密测量,再通过加热或溶剂溶解实现载具解键合,最终通过超声检测、应力分析等手段完成质量管控。

四、技术路线选择:效率、精度与成本的博弈模型

不同减薄技术在半导体制造中形成差异化应用矩阵,其技术特性与适用场景呈现显著差异:

机械研磨技术:基于金刚石砂轮的物理磨削原理,具备效率高、成本低的优势,适用于常规封装场景(100200μm厚度需求),但存在引入机械应力与表面损伤的风险。

化学机械抛光(CMP):通过化学腐蚀与机械抛光的协同作用,可实现亚微米级平坦度(<1μm),是3DTSV等先进封装工艺的核心技术,但面临设备成本高、加工速度慢的挑战。

湿法蚀刻技术:利用化学溶液的选择性腐蚀特性,可实现纳米级精度控制且无机械应力,适用于MEMS传感器、超薄芯片(<50μm)等场景,但需配套掩膜工艺与复杂环保处理流程。

干法刻蚀与激光减薄:前者通过等离子体轰击实现各向异性刻蚀,适用于2.5D封装微孔加工;后者以激光烧蚀实现局部精准减薄,在射频器件等特殊领域展现非接触加工优势,但存在热影响区(HAZ)与成本较高的技术瓶颈。

五、划片工艺的技术适配:以SDM-1型晶圆划片机为例

在晶圆减薄工艺完成后,划片(切割成单颗芯片)是封装阶段的关键工序,其精度直接影响芯片良率与性能。SDM-1型晶圆划片机作为典型设备,展现了减薄后加工的技术特性:

技术架构与适用范围

该设备采用集成光学与激光设计,可对2-6英寸(150mm)规格的硅、化合物半导体等材料基片进行激光划片,尤其适配减薄后厚度在100-600μm的晶圆。其核心技术——SD隐形切割工艺,通过1064nm波长激光实现非接触式加工,避免传统机械切割的崩边风险,特别适合超薄晶圆(如减薄至100μm的芯片)的精密分离。

精密定位与运动控制

设备搭载双路CCD视觉定位系统:旁轴CCD视野范围8*7mm(分辨率10μm)用于全局对准,同轴CCD配合50倍光学镜头(NA:0.42)实现切割道的微米级识别。动态聚焦系统采用压电陶瓷驱动,以10nm分辨率实现100μm行程内的实时焦距校正,配合±1.3mm范围的焦点跟随功能(分辨率0.25μm),可动态补偿晶圆表面起伏,确保切割深度均匀性。

运动精度与工艺效率

X/Y轴直线运动行程分别达300mm/150mm,速度≥500mm/s,定位精度±2.5μm,重复精度±1μm;Z轴(垂直方向)定位精度±2μm,满足不同厚度晶圆的聚焦需求。转台(O轴)支持±120°角度范围与600rpm转速,可实现斜切、圆弧切割等复杂路径加工,配合8轴运动控制系统,支持多组切割程序的自动切换。

工业级应用特性

设备采用紧凑式一体机设计(尺寸11008001700mm,重量≤450kg),支持手动上料与64路I/O控制,适用于中小批量生产场景。其纯净水冷却系统与0.5-0.7MPa压缩空气要求,体现了半导体设备对环境稳定性的标准需求。

六、未来技术演进:超薄化、高精度与绿色制造的三重挑战

随着摩尔定律渐近物理极限,先进封装技术(如3DIC、Chiplet)对晶圆减薄提出更高要求:3D堆叠场景需要将晶圆厚度控制在20μm以下,且整片晶圆厚度均匀性误差需小于1%;Chiplet技术则要求实现同一晶圆不同区域的差异化减薄,精度需达到微米级。与此同时,行业面临环保技术升级压力,无废水蚀刻、可回收磨料等绿色工艺成为研发重点,而激光诱导剥离、原子层蚀刻(ALE)等新兴技术正逐步从实验室走向工程化应用。

从微米尺度到纳米精度,从单一工艺到多元技术协同,晶圆减薄的技术演进史,本质是半导体行业突破物理极限的缩影。这项以“减薄”为核心特征的制造工艺,不仅精准调控着硅片的物理厚度,更深刻影响着芯片性能的演进方向——当晶圆厚度趋近于原子尺度,其背后折射的,是人类对精密制造技术边界的持续探索与突破。

-

超硬AR与普通AR抗反射膜的核心差异解析

在光学显示与光学器件领域,AR抗反射膜作为提升画面清晰度、优化光学性能的关键组件,应用场景日益广泛。目前市场上的AR抗反射膜主要分为普通AR与超硬AR两类,二者虽均以“减反增透”为核心目标,但在性能表现、适用场景等方面存在显著差距。本文结合膜层材料、结构设计、工艺路线等核心维度,系统解析两类AR膜的本质区别,为行业应用与选型提供参考。

2026-04-10

-

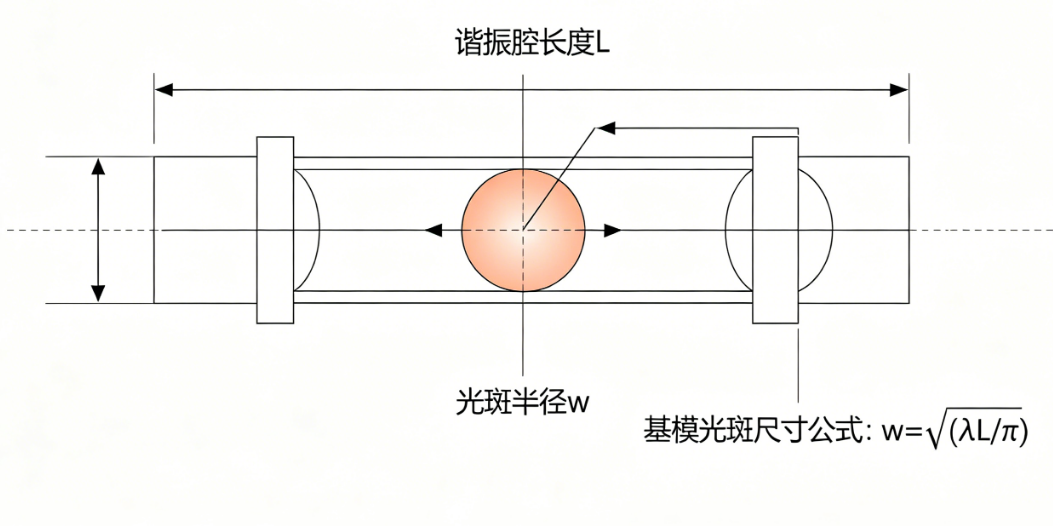

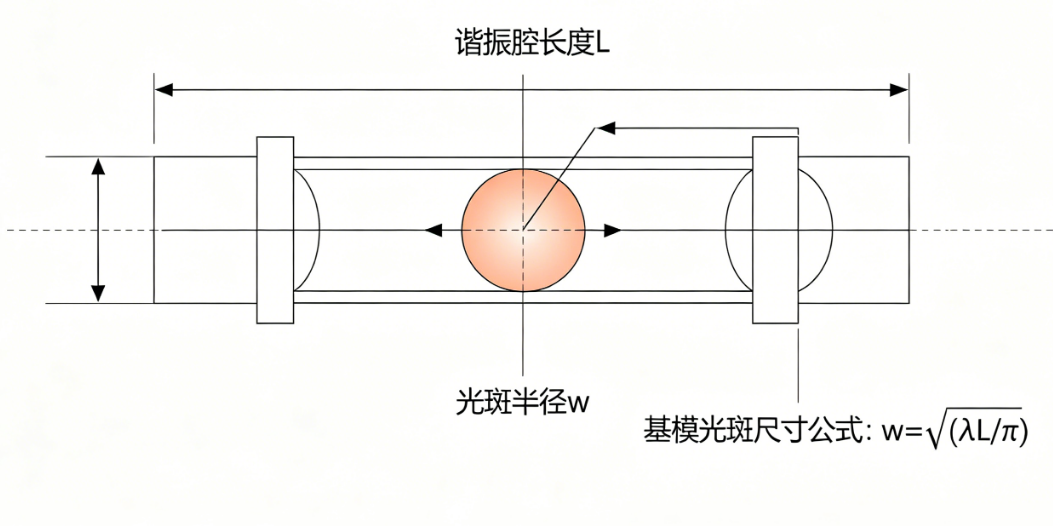

固体激光器谐振腔内光斑尺寸计算方法及工程应用

在固体激光器设计与性能优化中,谐振腔内光斑大小分布是决定光束质量、元件耐受功率及系统稳定性的核心参数。受增益介质热效应、腔型结构与光学元件排布等因素影响,腔内光斑尺寸并非固定值,需通过系统化建模与传输计算实现精准求解。本文基于热透镜等效模型与ABCD传输矩阵理论,系统阐述固体激光器谐振腔内光斑尺寸的完整计算流程、稳定性判据及工程应用价值,为激光器光学设计提供理论参考。

2026-04-10

-

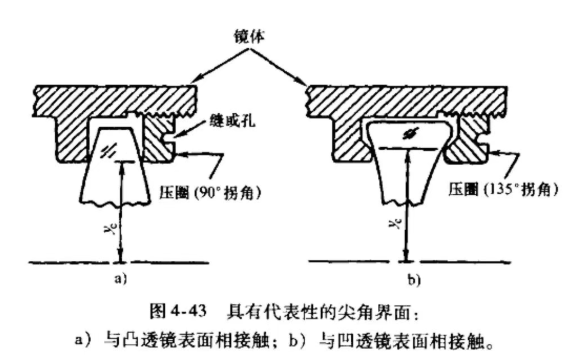

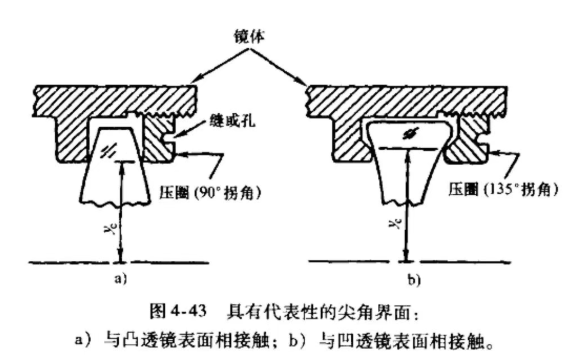

光学镜头装配中的5种光机界面接触方式:原理、特性与工程应用

光学镜头的装配精度直接决定了成像系统的最终性能,而光机界面作为光学元件与机械支撑结构的连接纽带,其设计与选择对同轴度控制、应力分布、热稳定性及长期可靠性具有决定性影响。在《光机系统设计》等权威著作中,将光机界面接触方式归纳为五大类:尖角界面、相切界面、超环面界面、球形界面及倾斜界面。本文系统解析这五种界面的设计原理、技术特性与工程应用场景,为光学工程师提供精准的选型参考。

2026-04-10

-

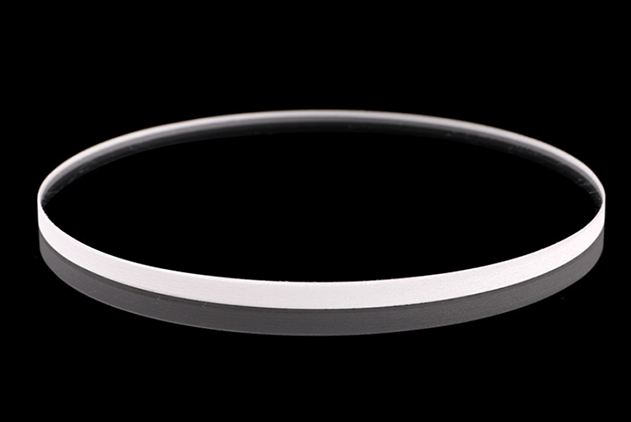

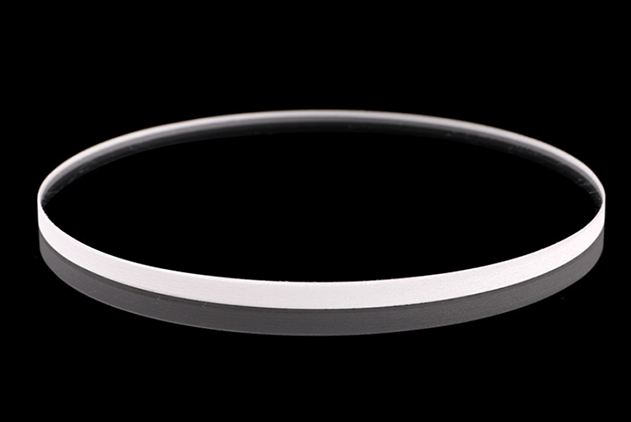

光学玻璃分类及K9玻璃特性解析

光学玻璃作为制造光学仪器核心部件的关键材料,广泛应用于光学透镜、棱镜、平面镜等产品的生产,其性能直接决定了光学仪器的成像质量与使用效果。本文将系统阐述光学玻璃的定义范畴、国家标准分类,并重点解析应用广泛的K9玻璃的核心特性,以及其与普通玻璃的本质区别

2026-04-09

-

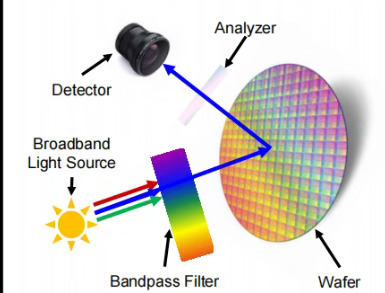

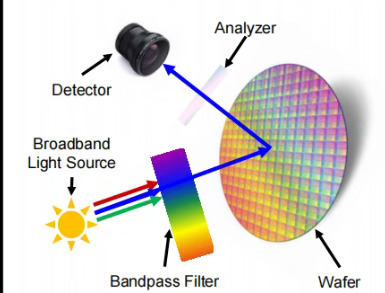

激光驱动光源(LDLS)技术原理及在半导体晶圆检测中的应用

随着半导体制造工艺持续向先进制程迭代,晶圆缺陷检测、薄膜厚度测量、光学计量等环节对光源的亮度、光谱范围、稳定性与空间相干性提出了愈发严苛的要求。传统氙灯、汞灯等常规光源在亮度、紫外输出及长期稳定性上已难以匹配高速、高精度检测需求。激光驱动光源(Laser-DrivenLightSource,LDLS)凭借超高亮度、宽谱连续输出与优异稳定性,成为先进半导体晶圆检测领域的核心关键光源,其技术特性与应用价值日益凸显。

2026-04-09